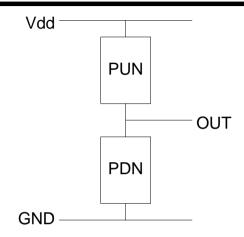

# Static CMOS Complementary Gates

#### • Static

After the appropriate propagation delay the ouput becomes valid and remains valid.<sup>1</sup>

#### Complementary

For any set of inputs there will exist either a path to Vdd or a path to GND.

Where this condition is not met we have either a high impedence output or a conflict in which the strongest path succeeds. Static CMOS Non-complementary gates make use of these possibilities.

<sup>&</sup>lt;sup>1</sup>c.f. Dynamic logic which uses circuit capicitance to store state for a short time.

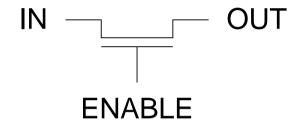

#### • Pass Transistor

- Provides very compact circuits.

- Good transmission of logic '0'.

- Poor transmission of logic '1'.

- - slow rise time

- - degradation of logic value

The pass transistor is used in many dynamic CMOS circuits<sup>2</sup>.

<sup>&</sup>lt;sup>2</sup>where pull-up is performed by an alternative method

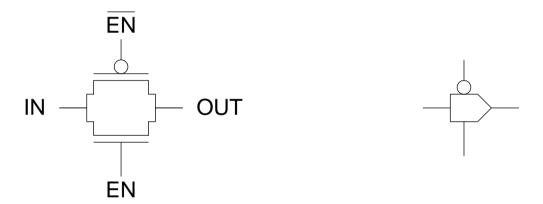

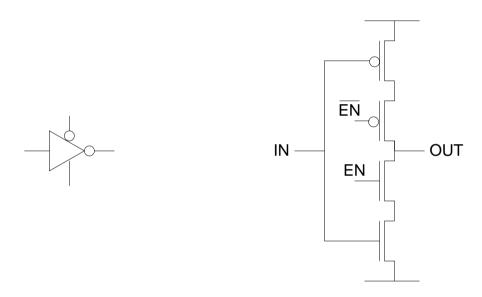

### • Transmission Gate

- For static circuits we would normally use a CMOS transmission gates:

- - balanced *n* and *p* pass transistors

- - faster pull-up

- - slower pull-down

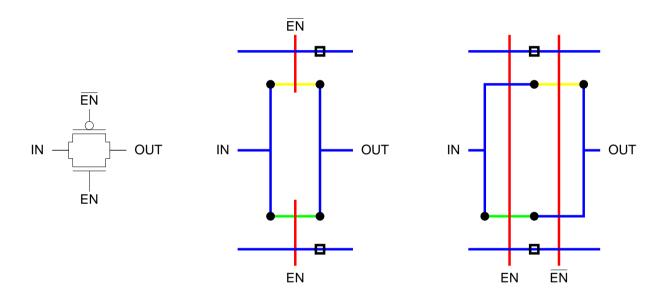

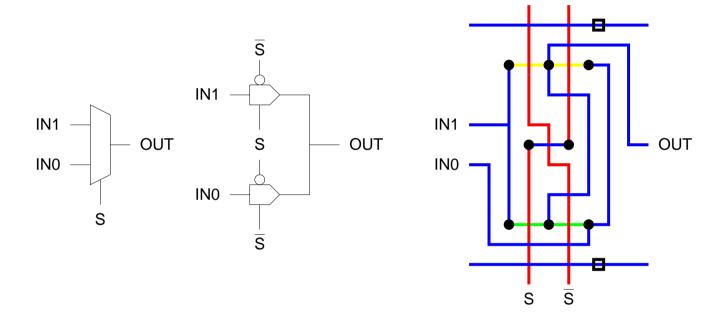

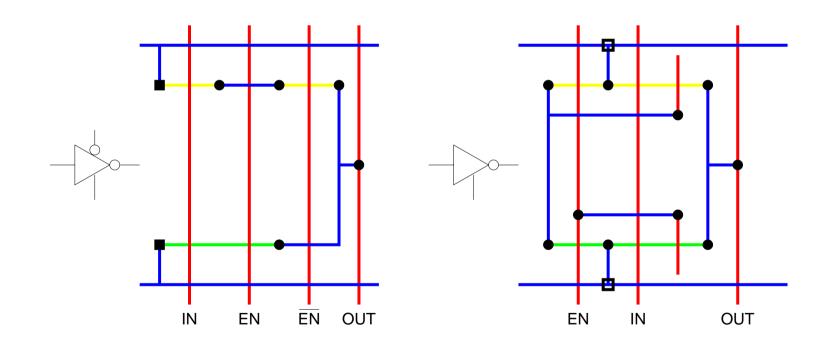

• Transmission Gate Layout

– note that these circuits are not fully complementary<sup>3</sup> hence they do not immediately lend themselves to a *line of diffusion* implementation.

<sup>&</sup>lt;sup>3</sup>since there are sets of inputs for which the output is neither pulled low nor high

# • Transmission Gate Multiplexor

- very few transistors 4 (+2 for inverter)

- difficult layout may offset this advantage

- - prime candidate for 2 level metal

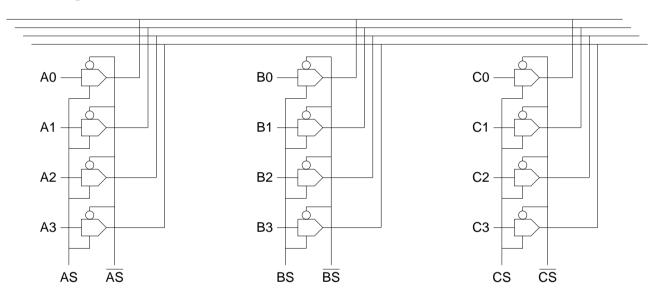

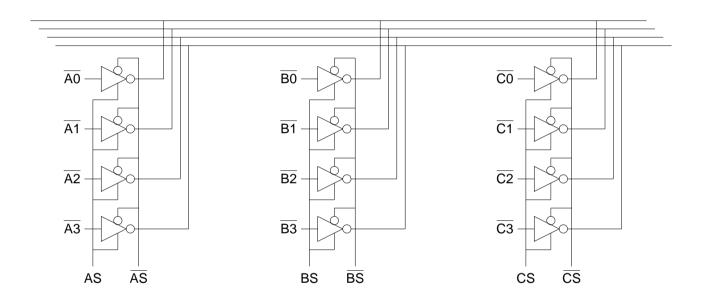

# • Bus Wiring

- distributed multiplexing<sup>4</sup>

- only one inverter required per bank of transmission gates

- greatly simplifies global wiring

<sup>&</sup>lt;sup>4</sup>internal chip bus should never be allowed to float high impedance

# Bus Distributed Multiplexing

Ideal for signals with many drivers from different modules.

# Bus Distributed Multiplexing

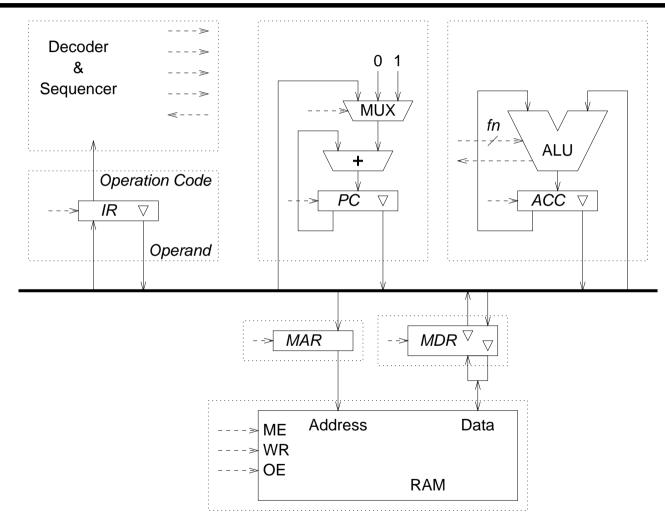

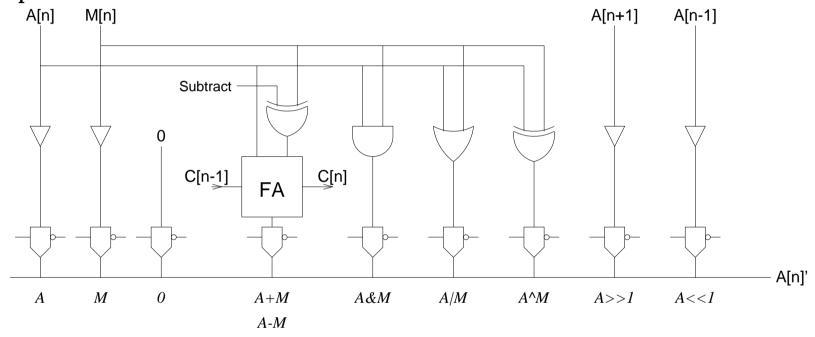

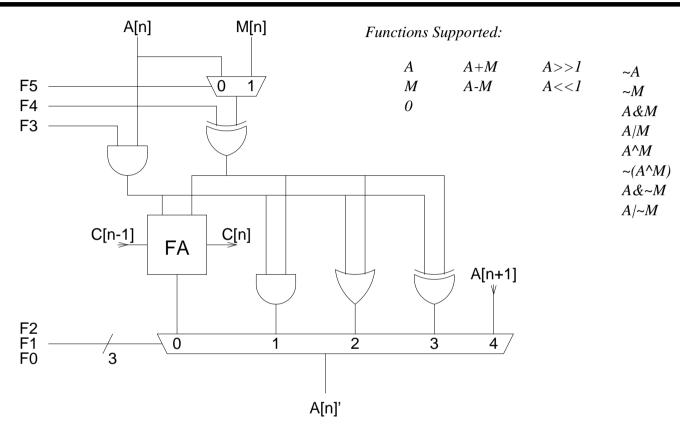

Implementation of bitslice ALU:<sup>5</sup>

- Separate circuit for each function

- Connected via distributed multiplexor

<sup>&</sup>lt;sup>5</sup>Note that transmission gates have no drive capability in themselves. Here a good drive is ensured by providing buffers.

# Bus Distributed Multiplexing

- Single optimized ALU module

- Multiplexing is not distributed

- Multiplexor implementation may use transmission gates

### • Tristate Inverter

– Any gate may have a tri-state output by combining it with a transmission gate.

### • Tristate Inverter

- Alternatively the transmission gate may be incorporated into the gate.

- - one connection is removed easier to layout

- - also easier to simulate!

# • Tristate Inverter Layout

#### • Tristate Inverter Bus Driver

- a tristate inverting buffer is often used to drive high capacitance bus signals

- transistors may be sized as required