This walkthough aims to introduce you to a simple ARM SoC and the hardware/software design flow.

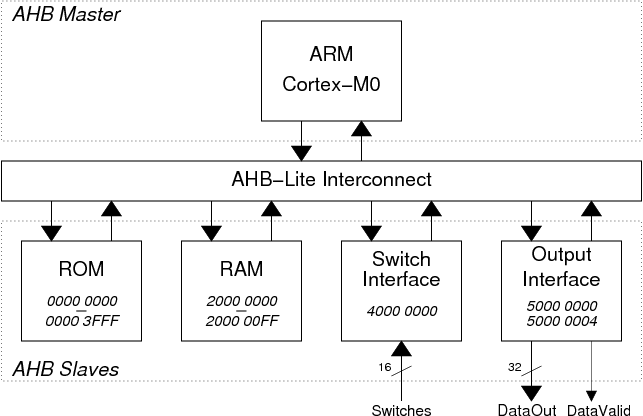

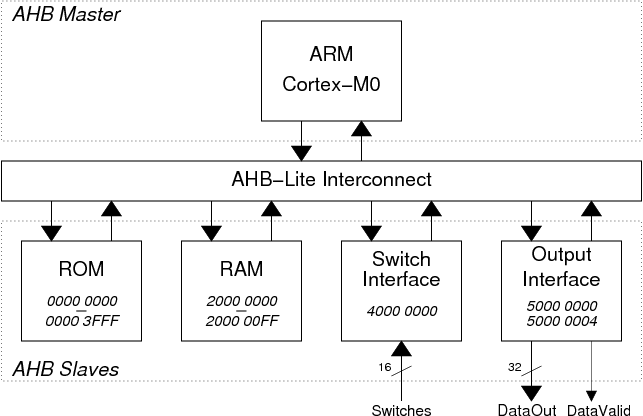

A very simple ARM System on Chip has been designed:

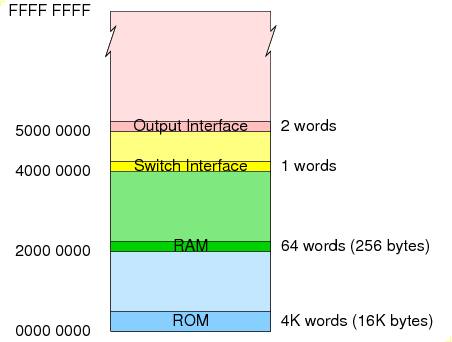

The secondary images are an artefact of the partial address decoding which only uses the top 4 address bits (HADDR[31:28]) in order to decide which slave is being accessed.

In order to build the ARM SoC, we need SystemVerilog files to model the hardware plus C program files and other support files to build the software. Further files are required to support simulation:

mkdir -p ~/design/system_on_chip/example

cd ~/design/system_on_chip/example

init_soc_example -here

Running the compile_and_link script:

cd software

./compile_and_link

should create a Verilog hex format file named "code.hex" which

can be used in simulation and synthesis.

cd ..

./simulate &

Note that because the stack grows downwards, the higher memory addresses are used before the lower ones.

The following actions should be possible without closing the simulation.

if ( switch_temp < 8 ) {

(which limits the range of number for which a factorial is calculated)

with this line:

if ( switch_temp < 16 ) {

and re-run the compile_and_link script.

Simulation -> Reinvoke Simulator...

dialogue to re-run the simulation using the newly updated code.hex file.

RAM (rwx) : ORIGIN = 0x20000000, LENGTH = 256(which tells the linker how much memory is provided) with this line:

RAM (rwx) : ORIGIN = 0x20000000, LENGTH = 1024

make clean ./compile_and_link

At this stage you can experiment with other changes to the system but you should try to make only small changes between simulations to increase the chances of being able to debug the system.

Iain McNally

22-2-2017