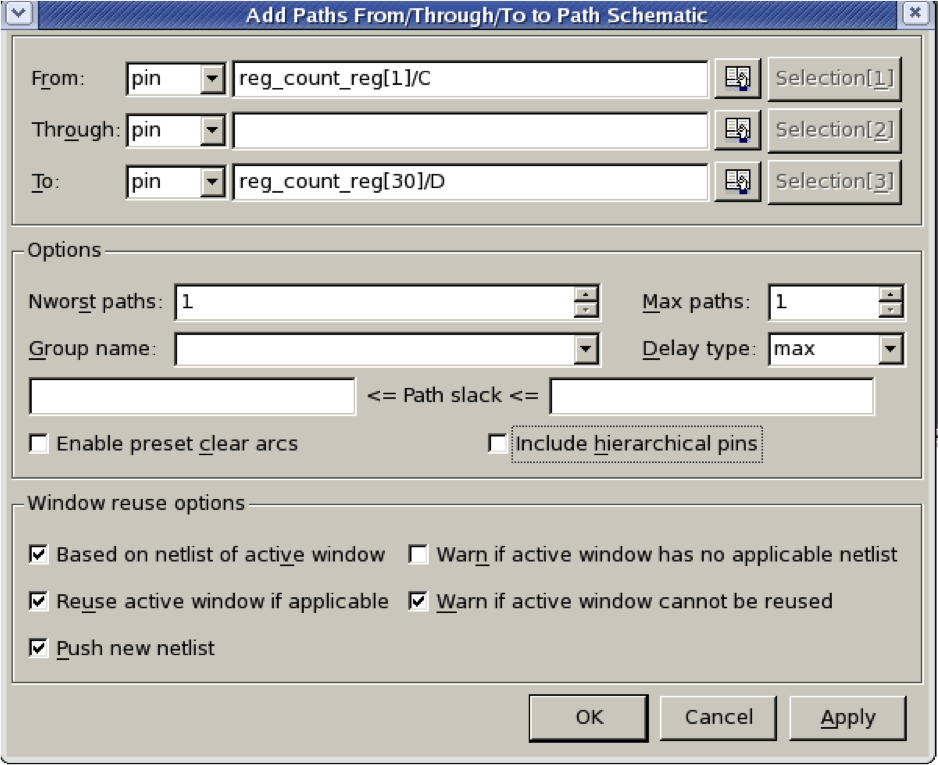

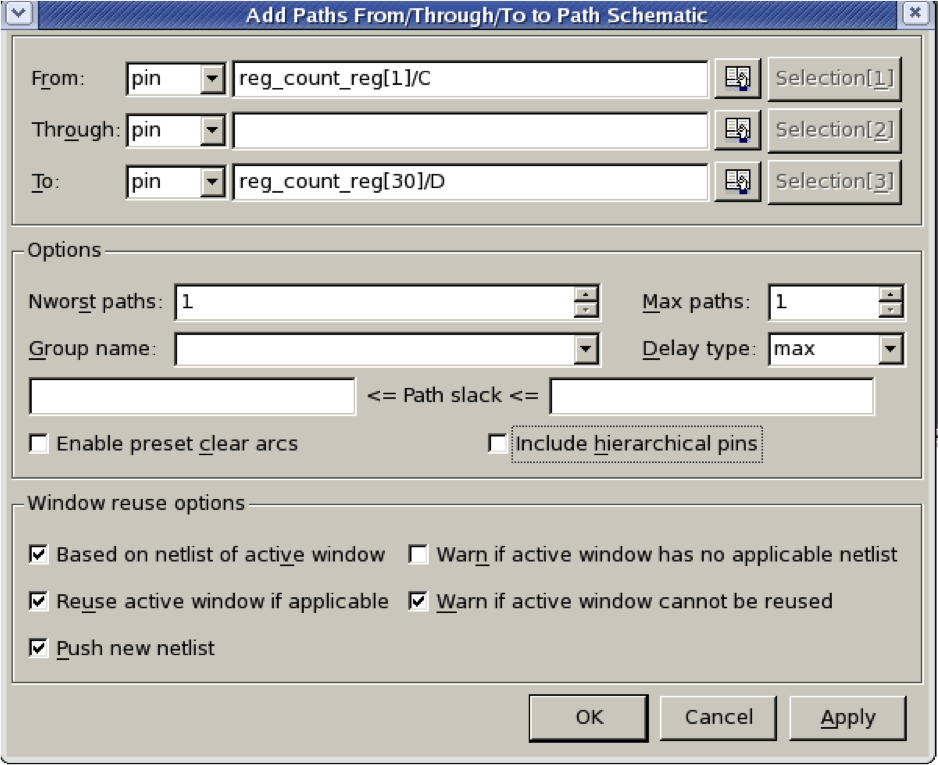

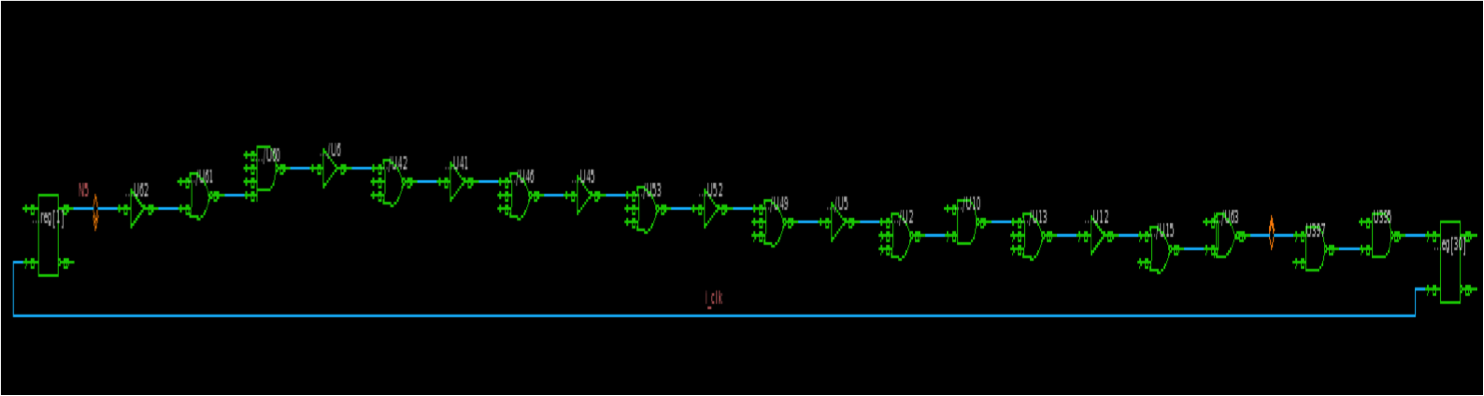

- In design vision: go to the Schematic menu and choose the option Add Paths From/To

- Fill in the starting point and end point of the critical path from the previous timing report

- Click ok

- Click ok again for the pop up window

After completing this unit, you should be able to:

For this lab you will need:

| Set up the library |

|---|

| Read in Design |

| Elaborate |

| Add Constraints |

| Map |

| Design Analysis |

| Timing Optimization |

| Design Write Out |

ams_demo

________________________|______________________

| | | |

behavioural constraints gate_level synthesis

dc_shell -gui

If you are logged into one of the Redhat 6 CAD servers (cadteaching, hart2 or hind2) the dc_shell command should already be in your search path and this command should run without any error messages (do not run any DC_Setup script).

If the .synopsys_dc.setup file is in the current working directory, the 0.35 um AMS technology library will automatically be loaded when dc_shell is invoked (there is no need to explicitly source any library setup file).

analyze -format sv "../behavioural/qmults.sv ../behavioural/wrap_qmults.sv"

Presto compilation completed successfully. 1

elaborate <modulename>

elaborate wrap_qmults

At this stage you can navigate through the hierarchy by double-clicking on sub-modules in order to descend into them and using the "Back" function on the right-button menu in order to ascend the hierarchy.

Before you go on with the lab, ensure that the top level module is selected again:

change_selection wrap_qmults

(failure to do this may result in the a program crash)

check_timing

Warning: the following end-points are not constrained for maximum delay. End point --------- complete ........ overflow result_out[1] result_out[0] ........

create_clock -period 20 -name master_clock [get_ports Clock]

set_max_area 0

This will instruct design compiler to use as little area as possible.

compile

To include a scan capable flip-flops, the command is:

compile -scan

This command may take a few minutes depending on the size of

the design.

To improve the testability of the fabricated chips (so we can quickly discard those with fabrication faults), we can get the tools to add Design For Test (DFT) structures to the existing design.

Using the procedure below, we can add a single scan path to our design. Although there are many more sophisticated DFT structures that we could consider, a single scan path is conceptually very simple and should be enough for most student designs.

This tells the which ports to use for the scan path control signals:

set_dft_signal -view existing_dft -type ScanClock -port <clock_port> -timing {45 60}

set_dft_signal -view existing_dft -type Reset -port <nreset_port> -active_state 0

set_dft_signal -view spec -type ScanEnable -port <test_port> -active_state 1

set_dft_signal -view spec -type ScanDataIn -port <sdi_port>

set_dft_signal -view spec -type ScanDataOut -port <sdo_port>

e.g.

set_dft_signal -view existing_dft -type ScanClock -port Clock -timing {45 60}

set_dft_signal -view existing_dft -type Reset -port nReset -active_state 0

set_dft_signal -view spec -type ScanEnable -port Test -active_state 1

set_dft_signal -view spec -type ScanDataIn -port SDI

set_dft_signal -view spec -type ScanDataOut -port SDO

set_dft_signal -view existing_dft -type ScanClock -port <clock_port> -timing {45 60}

set_dft_signal -view existing_dft -type Reset -port <nreset_port> -active_state 0

set_dft_signal -view spec -type TestMode -port <test_port> -active_state 1

set_dft_signal -view spec -type ScanEnable -port <scan_enable_port> -active_state 1

set_dft_signal -view spec -type ScanDataIn -port <sdi_port>

set_dft_signal -view spec -type ScanDataOut -port <sdo_port>

e.g.

set_dft_signal -view existing_dft -type ScanClock -port Clock -timing {45 60}

set_dft_signal -view existing_dft -type Reset -port nReset -active_state 0

set_dft_signal -view spec -type TestMode -port Test -active_state 1

set_dft_signal -view spec -type ScanEnable -port ScanEnable -active_state 1

set_dft_signal -view spec -type ScanDataIn -port SDI

set_dft_signal -view spec -type ScanDataOut -port SDO

Having separate Test and ScanEnable ports allows the system to be in Test mode without

the scan path being configured.

For the qmults example the simple five-ports configuration should work (Clock, nReset, Test, SDI, SDO).

create_test_protocol

dft_drc

If this DFT design rule check throws up errors you may need to go back and edit your SystemVerilog code or else ask the tool to try and fix the problem.

Violations relating to reset/set may occur if you include a reset synchroniser in your design. The following code should help the tool to fix these problems:

set_dft_configuration -fix_reset enable

set_autofix_configuration -type reset -method mux -control Test -test_data nReset

set_dft_configuration -fix_set enable

set_autofix_configuration -type set -method mux -control Test -test_data nReset

Note that this more advanced "mux" fix method is only available if you have separate "ScanEnable" and "Test" ports

set_scan_configuration -chain_count 1

preview_dft

insert_dft

report_qor

This will provide information about the timing information, critical path slack,

critical path clock period, total design area and information about the CPU statistics.

report_power

This will provide information about dynamic and leakage power.

report_timing

report_area > synth_area.rpt

report_power > synth_power.rpt

report_timing > synth_timing.rpt

It is important to ensure that the naming styles of variable in the design are appropriatefor the target output language we are using (Verilog in this case). We can firstly see what names need changing:

report_names -rules verilog

If we are happy with the proposed new names we can perform the name changing process:

change_names -rules verilog -hierarchy -verbose

This is the final step in the synthesis flow, it allows the designer to transfer the synthesised circuit to the next stage of the design flow. This can be done as follows:

write -f verilog -hierarchy -output "../gate_level/wrap_qmults.v"

write_sdc ../constraints/wrap_qmults.sdc

write -f verilog -hierarchy -output "../gate_level/wrap_qmults.v"

write_sdf ../gate_level/wrap_qmults.sdf

analyze -format sv "../behavioural/qmults.sv ../behavioural/wrap_qmults.sv"

elaborate wrap_qmults

create_clock -name master_clock -period 20 [get_ports Clock]

compile

report_area > synth_area.rpt

report_power > synth_power.rpt

change_names -rules verilog -hierarchy -verbose

write -f verilog -hierarchy -output "../gate_level/wrap_qmults.v"

write_sdc ../constraints/wrap_qmults.sdc

write_sdf ../gate_level/wrap_qmults.sdf

exit

There are many ways in which a designer can tweak the design at the synthesis stage to obtain the target performance :

compile -map_effort high

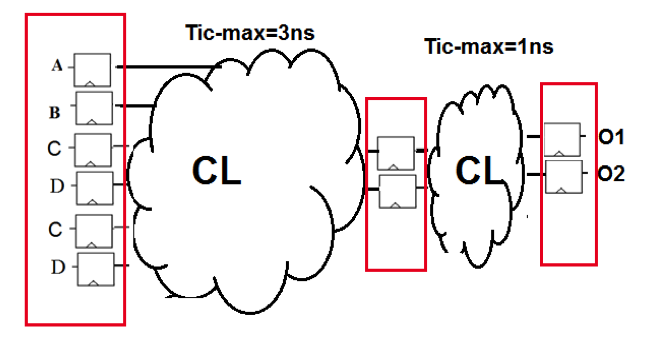

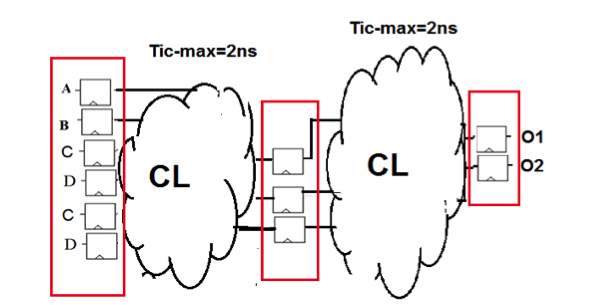

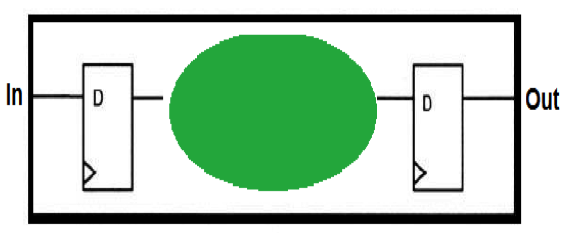

balance_registers

|

=> |  |

|

=> |  |

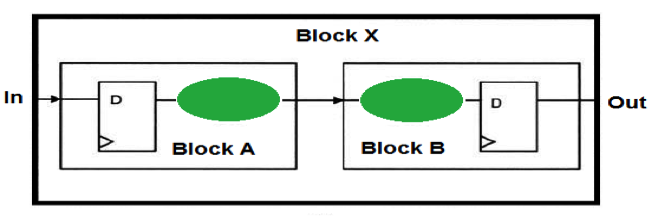

current_design <modulename>

ungroup -all -flatten

compile -map_effort high -incremental_mapping

However, this option is not suitable for usage if the hierarchical design is large.

Too huge a design will take up considerable computing resources

(for example, a long time to compile).

set_implementation <implementation_type> <cell_list>

set_implementation cla A1

| Implementation type | Description |

|---|---|

| rpl | Ripple carry |

| cla | Carry look ahead |

| clf | Fast carry look ahead |

| sim | Simulation model |

report_resources

remove_attribute [get_cells *] implementation

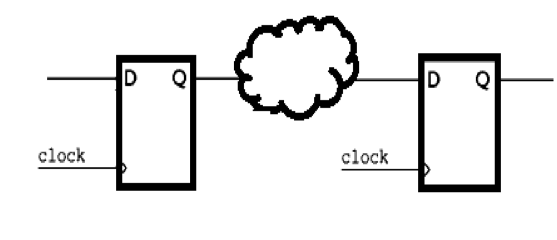

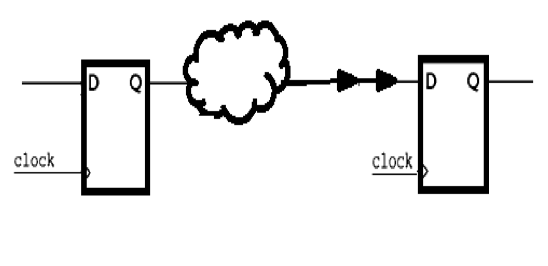

|

=> |  |

set_fix_hold <clock_name>

compile -map_effort high -incremental_mapping

set_fix_hold clk1

remove_attribute [get_clocks clk1] fix_hold