# Programming in C and Interrupts

# **Design Summary**

# Design Summary

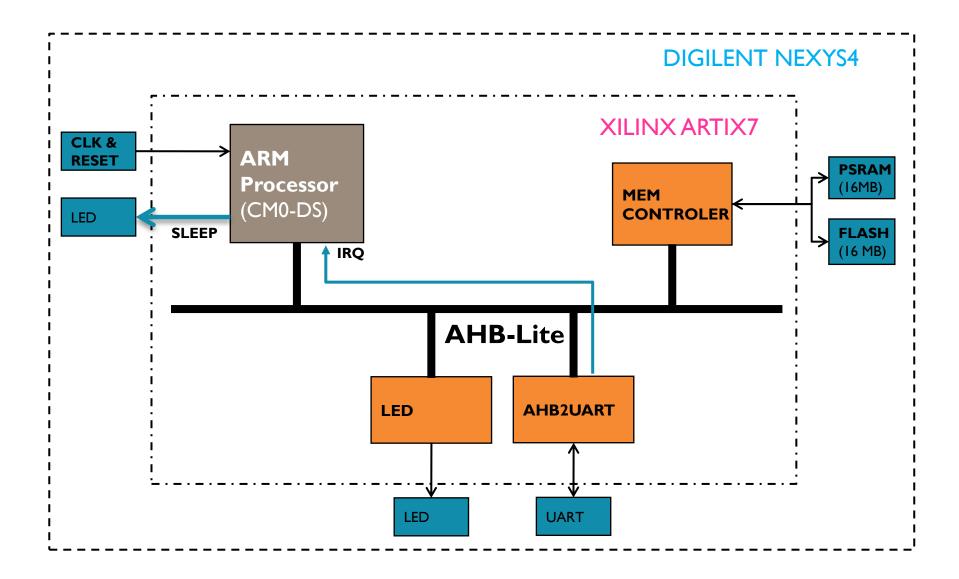

The design consists of 3 peripherals with below memory map

|                    | Base Address | Size                                                                 |

|--------------------|--------------|----------------------------------------------------------------------|

| PSRAM/Internal Ram | 0×0000_0000  | 8 MB/16KB                                                            |

| LED                | 0×5000_0000  | 0x00 General Purpose IO                                              |

| UART               | 0x5100_0000  | 0x00 Send/Receive<br>0x04 Control Register<br>Can generate Interrupt |

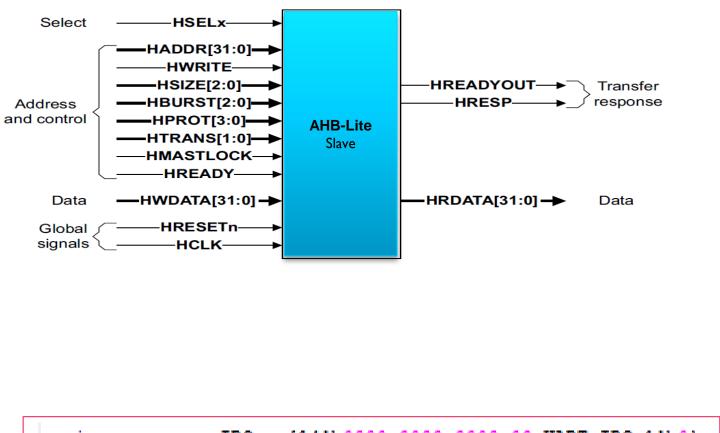

### **AHB Slaves**

| AHBUART uAHBUART (           |

|------------------------------|

| .HCLK(HCLK),                 |

| .HRESETn(HRESETn),           |

| .HADDR(HADDR[31:0]),         |

| .HTRANS(HTRANS[1:0]),        |

| .HWDATA(HWDATA[31:0]),       |

| .HWRITE(HWRITE),             |

| .HREADY (HREADY) ,           |

| .HREADYOUT (HREADYOUT_UART), |

| .HRDATA(HRDATA_UART[31:0]),  |

| .HSEL (HSEL_UART) ,          |

|                              |

| .RsRx (RsRx) ,               |

| .RsTx(RsTx),                 |

| .uart_irq(UART_IRQ)          |

| );                           |

assign

IRQ = {14'b0000\_0000\_0000\_00,UART\_IRQ,1'b0};

# ARMv6-M Exception Model

| Exception number | Exception type          | Priority     |

|------------------|-------------------------|--------------|

| T                | Reset                   | -3 (highest) |

| 2                | NMI                     | -2           |

| 3                | HardFault               | -1           |

| 4-10             | Reserved                |              |

| П                | SVCall                  | Programmable |

| 12-13            | Reserved                |              |

| 14               | PendSV                  | Programmable |

| 15               | SysTick, optional       | Programmable |

| 16 + N           | External interrupt 0-31 | Programmable |

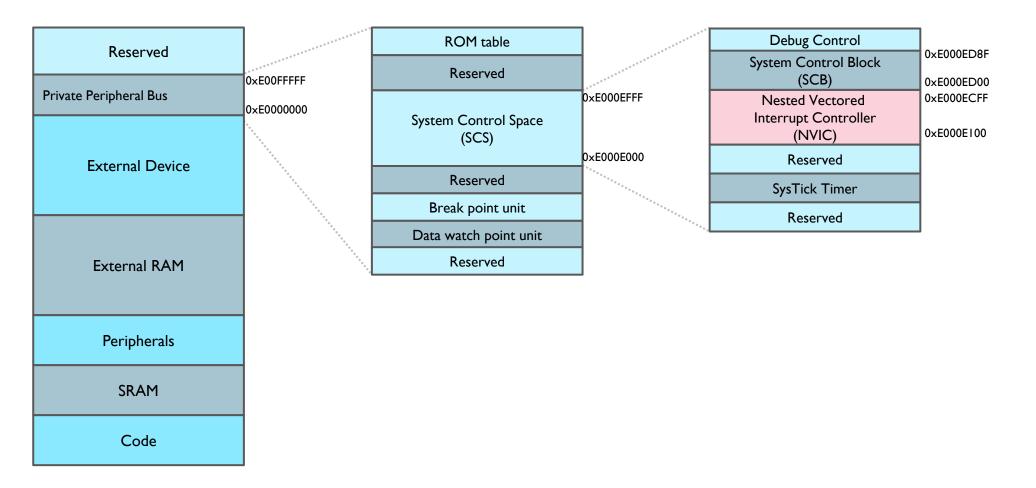

### **Cortex-M0 Interrupt Controller**

- Nested Vectored Interrupt Controller (NVIC)

- An integrated part of the Cortex-M0 processor;

- Supports up to 32 IRQ inputs and a non-maskable interrupt (NMI) inputs;

- Flexible interrupt management

- Enable/ disable interrupt;

- Pending control;

- Priority configuration;

- Hardware nested interrupt support;

- Vectored exception entry;

- Interrupt masking;

- Can be easily accessed using C or assembly language.

- Location: Private Peripheral Bus  $\rightarrow$  System Control Space  $\rightarrow$ NVIC

# Cortex-M0 Interrupt Controller

Memory map of Nested Vectored Interrupt Controller (NVIC)

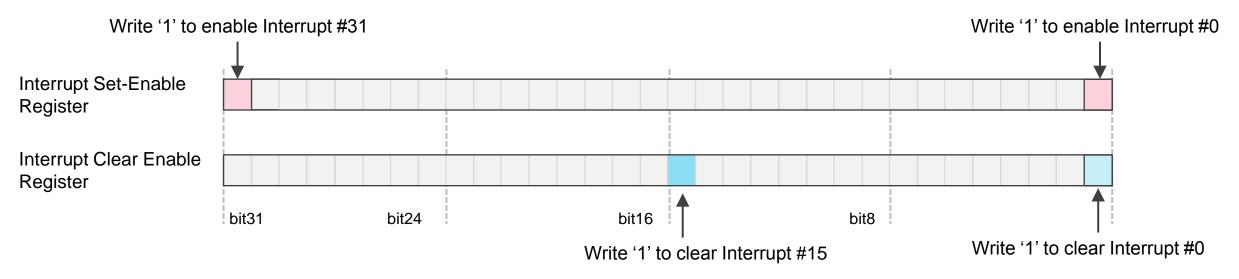

# **NVIC Registers**

| Address                 | Register                         |

|-------------------------|----------------------------------|

| 0xE000E100              | Interrupt Set-Enable Register    |

| 0×E000E104 — 0×E000E17F | Reserved                         |

| 0xE000E180              | Interrupt Clear-Enable Register  |

| 0×E000E184 — 0×E000E1FF | Reserved                         |

| 0xE000E200              | Interrupt Set-Pending Register   |

| 0×E000E204 — 0×E000E27F | Reserved                         |

| 0xE000E280              | Interrupt Clear-Pending Register |

| 0×E000E300 — 0×E000E3FC | Reserved                         |

| 0xE000E400 — 0xE000E41C | Interrupt Priority Registers     |

| 0xE000E420 — 0xE000E43C | Reserved                         |

### **NVIC Registers**

- Interrupt Set-Enable Register

- Write 'I' to enable one or more interrupts;

- Write '0' has no effect;

- Interrupt Clear Enable Register

- Write 'I' to Clear one or more interrupts.

- Write '0' has no effect;

### **NVIC Registers**

#### Why use separated register address

- Compared with the "read-modify-write" process the benefit of using separated address includes:

- Reduces the steps needed for enabling/ disabling an interrupt, resulting in smaller code and less execution time;

- Prevents the race condition, e.g. the main thread is accessing a register by "read-modify-write" process, and it is interrupted between its "read" and "write" operation. If the ISR again modifies the same register that is currently being accessed by the main thread, a conflict will occur.

#### Interrupt pending and clear pending

• An interrupt goes into pending status if it cannot be processed immediately, e.g. a lower priority interrupt will be pended if a higher interrupt is being processed.

### Enabling UART Interrupt

```

#define AHB LED BASE

0x50000000

8

#define AHB UART BASE

0x51000000

9

0xE000E100

#define NVIC INT ENABLE

10

11

12

volatile static int counter=0x31;

13

14

void UART ISR()

15 - {

16

char c;

17

c=*(unsigned char*) AHB UART BASE; //read a character from UART

* (unsigned char*) AHB UART BASE = c; //write the character to UART

18

19

}

20

21

22

// Main Function

23

24

25

26 [int main(void) {

volatile int i;

27

28

int delay = 10000;

29

30

*(unsigned int*) NVIC INT ENABLE = 0x00000002;

//Enable interrupts for UART

* (volatile unsigned int*) AHB LED BASE = 0xAA;

31

32

33 📄

while(1){

```

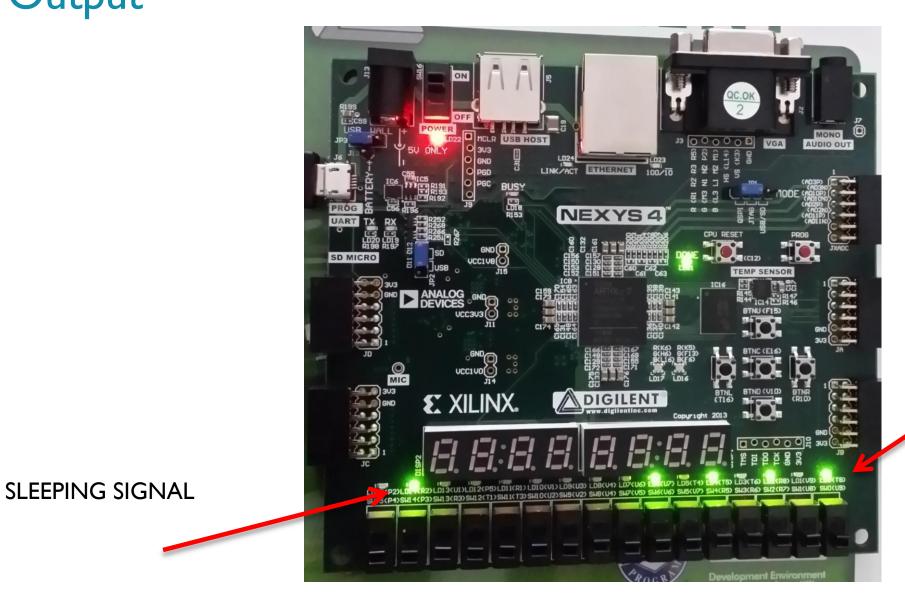

### WFI (Wait for Interrupt) Instruction

- When the processor executes a WFI it stops executing instructions and enters sleep mode.

- The Processor stays in SLEEP mode until one of the following event occurs,

- a non-masked interrupt occurs and is taken

- an interrupt masked by PRIMASK becomes pending

- a Debug Entry request.

- When the processor enters "SLEEP" mode, the "SLEEPING" sideband signal is asserted from Cortex M0

- This signal is used to implement various hardware power saving techniques

# WFI (Wait for Interrupt) Instruction

```

_____

22

23

// Main Function

24

25

26 [int main(void) {

27

volatile int i;

28

int delay = 10000;

29

30

*(unsigned int*) NVIC INT ENABLE = 0x00000002;

//Enable interrupts for UART

31

*(volatile unsigned int*) AHB LED BASE = 0xAA;

32

33 🗄

while(1){

34

35

// Do some processing before entering Sleep Mode

36

37

*(volatile unsigned int*) AHB LED BASE = ~ *(volatile unsigned int*) AHB LED BASE;

Processor Busy

for(i=0;i<delay;i++);</pre>

38

*(volatile unsigned int*) AHB LED BASE = ~ *(volatile unsigned int*) AHB LED BASE;

39

40

for(i=0;i<delay;i++);</pre>

*(volatile unsigned int*) AHB LED BASE = ~ *(volatile unsigned int*) AHB LED BASE;

41

42

for(i=0;i<delay;i++);</pre>

43

44

// Enter Sleep MODE

45

wfi();

46

Enter SLEEP Mode and wait

47

48

until UART interrupts

49

```

# Calling a C Function from Assembly

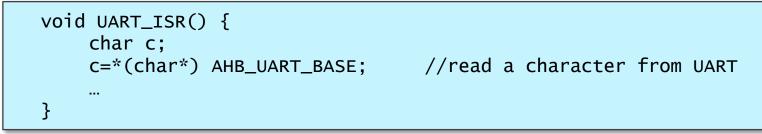

ISR can be written in either assembly or C language, for example in C:

• Call a C function from the assembly code, for example:

| BL UART_ISR // branch to ISR written in C<br>POP {R0,R1,R2,PC} // context restoring | UART_Handler | PROC<br>EXPORT UART_Handler // label name in assembly<br>IMPORT UART_ISR // function name in C<br>PUSH {R0,R1,R2,LR}// context saving |

|-------------------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                     |              | BL UART_ISR // branch to ISR written in C                                                                                             |

### Retarget printf

```

#include <rt misc.h>

4

5

6

#define AHB LED BASE

0x50000000

7 #define AHB UART BASE

0x51000000

8 #define AHB UART STATUS

0x51000004

9

10

#pragma import( use no semihosting)

11

12 struct FILE {

13

unsigned char * ptr;

14

};

15

FILE stdout = {(unsigned char *) AHB UART BASE};

16

FILE stdin =

17

{ (unsigned char *) AHB UART BASE};

18

19

int uart out(int ch)

20 - {

21

22

volatile unsigned char* UARTBase;

23

volatile unsigned char* UARTStatus;

UARTBase = (volatile unsigned char*)AHB UART BASE;

24

UARTStatus = (volatile unsigned char*)AHB UART STATUS;

25

26

*UARTBase = (char)ch;

27

while((*UARTStatus & 0x2) == 0x1); // Wait until its sent

28

return(ch);

29

3

30

31

32

int fputc(int ch, FILE *f)

33 - {

34

return(uart out(ch));

35

36

~ -

```

ARM

### Lab Steps (with PSRAM)

- I. Compile the Software using KEIL MDK ARM and generate code.hex file

- 2. Follow the steps given in the lab manual to download code.hex onto PSRAM

- 3. Open FPGA project under Vivado and implement the design

- 4. Use Vivado hardware manager to download the .bit file

- 5. Communicate with the board using HyperTerminal (or any other serial terminal)

### Lab Steps (with BRAM)

- I. Compile the Software using KEIL MDK ARM and generate code.hex file

- 2. Open FPGA project under Vivado and implement the design

- 3. Use Vivado hardware manager to download the .bit file

- 4. Communicate with the board using HyperTerminal (or any other serial terminal)

### Output

LEDs change pattern when you send UART Characters.