#### ARM Cortex<sup>®</sup>- M0 Processor Core

An Overview

The Architecture for the Digital World®

#### **ARM Processors Portfolio**

| Processor<br>Class | ARM Processor       | Architecture | Performance<br>DMIPS/MHz | <b>ARM</b> instructions | Thumb-2 instructions | Jazelle-DBX JAVA<br>bytecode execution | Jazelle-RCT Dynamic<br>compiler support | TrustZone security | E' DSP extensions | Media SIMD<br>extensions | NEON SIMD<br>extensions | Floating point | Caches | Memory Management<br>Unit (MMU) | Memory Protection<br>Unit (MPU) | Hardware Cache<br>coherency | Target OS    | Trace support       |

|--------------------|---------------------|--------------|--------------------------|-------------------------|----------------------|----------------------------------------|-----------------------------------------|--------------------|-------------------|--------------------------|-------------------------|----------------|--------|---------------------------------|---------------------------------|-----------------------------|--------------|---------------------|

|                    | ARM7TDMI/ARM7TDMI-S | ARMv4-T      | 0.95                     | ~                       | ×                    | ×                                      | ×                                       | ×                  | ×                 | ×                        | ×                       | ×              | ×      | ×                               | ×                               | ×                           | Real Time    | ~                   |

|                    | ARM946E-S           | ARMv5-E      | 1.23                     | ~                       | ×                    | ×                                      | ×                                       | ×                  | ~                 | ×                        | ×                       | Optional       | ~      | ×                               | ~                               | ×                           | Real Time    | ~                   |

| ARM7               | ARM926EJ-S          | ARMv5-EJ     | 1.06                     | ~                       | ×                    | ~                                      | ×                                       | ×                  | ~                 | ×                        | ×                       | Optional       | ~      | ~                               | ×                               | ×                           | Platform     | ~                   |

| ARM9               | ARM1136J-S          | ARMv6        | 1.18                     | ~                       | ×                    | ~                                      | ×                                       | ×                  | ~                 | ~                        | ×                       | Optional       | ~      | ~                               | ×                               | ×                           | Platform     | ~                   |

|                    | ARM1156T2-S         | ARMv6-T2     | 1.45                     | ~                       | ~                    | ×                                      | ×                                       | ×                  | ~                 | ~                        | ×                       | Optional       | ~      | ×                               | ~                               | ×                           | Real Time    | ~                   |

| ARMII              | ARM1176JZ-S         | ARMv6-Z      | 1.26                     | ~                       | ×                    | ~                                      | ×                                       | ~                  | ~                 | ~                        | ×                       | Optional       | ~      | ~                               | ×                               | ×                           | Platform     | ~                   |

|                    | ARM11 MPCore        | ARMv6        | 1.25                     | ~                       | ×                    | ~                                      | ×                                       | ×                  | ~                 | ~                        | ×                       | Optional       | ~      | ~                               | ×                               | ~                           | Platform/SMP | ~                   |

|                    | Cortex-M0+          | ARMv6-M      | 0.90                     | ×                       | ~                    | ×                                      | ×                                       | ×                  | ×                 | ×                        | ×                       | ×              | ×      | ×                               | ×                               | ×                           | Real Time    | ×                   |

|                    | Cortex-M0           | ARMv6-M      | 0.90                     | ×                       | ~                    | ×                                      | ×                                       | ×                  | ×                 | ×                        | ×                       | ×              | ×      | ×                               | ×                               | ×                           | RealTime     | ×                   |

|                    | Cortex-M1           | ARMv6-M      | 0.79                     | ×                       | ×                    | ×                                      | ×                                       | ×                  | ×                 | ×                        | ×                       | ×              | ×      | ×                               | ×                               | ×                           | Real Time    | ×                   |

|                    | Cortex-M3           | ARMv7-M      | 1.25                     | ×                       | ~                    | ×                                      | ×                                       | ×                  | ×                 | ×                        | ×                       | ×              | ×      | ×                               | Optional                        | ×                           | RealTime     | Instruction<br>only |

|                    | Cortex-M4           | ARMv7-ME     | 1.25                     | ~                       | ~                    | ×                                      | ×                                       | ×                  | ~                 | ~                        | ×                       | Optional       | ~      | ×                               | Optional                        | ×                           | Real Time    | ~                   |

|                    | Cortex-A5 MPCore    | ARMv7+MP     | 1.58                     | ~                       | ~                    | ~                                      | ~                                       | ~                  | ~                 | ~                        | Optional                | Optional       | ~      | ~                               | ×                               | ✓+ACP                       | Platform/SMP | ~                   |

|                    | Cortex-R4           | ARMv7        | 1.66                     | ~                       | ~                    | ×                                      | ×                                       | ×                  | ~                 | ~                        | ×                       | Optional       | ~      | ×                               | Optional                        | ×                           | Real Time    | ~                   |

|                    | Cortex-R5           | ARMv7        | 1.66                     | ~                       | ~                    | ×                                      | ×                                       | ×                  | ~                 | ~                        | ×                       | Optional       | ~      | ×                               | Optional                        | ×                           | Real Time    | ~                   |

|                    | Cortex-R7           | ARMv7        | 2.53                     | ~                       | ~                    | ×                                      | ×                                       | ×                  | ~                 | ~                        | ×                       | Optional       | ~      | ×                               | Optional                        | ×                           | Real Time    | ~                   |

|                    | Cortex-A7           | ARMv7+MP     | 1.90                     | ~                       | ~                    | ~                                      | ~                                       | ~                  | ~                 | ~                        | ~                       | ~              | ~      | ~                               | ×                               | ✓+ACP                       | Platform/SMP | PTM                 |

|                    | Cortex-A8           | ARMv7        | 2.07                     | ~                       | ~                    | ~                                      | ~                                       | ~                  | ~                 | ~                        | ~                       | ~              | ~      | ~                               | ×                               | ×                           | Platform     | ~                   |

|                    | Cortex-A9 MPCore    | ARMv7+MP     | 2.50                     | ~                       | ~                    | ~                                      | ~                                       | ~                  | ~                 | ~                        | Optional                | Optional       | ~      | ~                               | ×                               | ✓+ACP                       | Platform/SMP | PTM                 |

|                    | Cortex-A15 MPCore   | ARMv7+MP     | 2.50                     | ~                       | ~                    | ~                                      | ~                                       | ~                  | ~                 | ~                        | ~                       | ~              | ~      | ~                               | ×                               | ✓+ACP                       | Platform/SMP | PTM                 |

|                    | Cortex-A53          | ARMv8        | 2.3                      | ~                       | ~                    | ~                                      | ~                                       | ~                  | ~                 | ~                        | ~                       | ~              | ~      | ~                               | ×                               | ✓+ACP                       | Platform/SMP | PTM                 |

|                    | Cortex-A57          | ARMv8        | >4.0                     | ~                       | ~                    | ~                                      | ~                                       | ~                  | ~                 | ~                        | ~                       | ~              | ~      | ~                               | ×                               | ✓+ACP                       | Platform/SMP | PTM                 |

## Equipment Adopting ARM Cores

## **ARM Cortex-M Series Family**

| Processor  | ARM<br>Architecture | Core<br>Architecture | Thumb <sup>®</sup> | Thumb <sup>®</sup> -2 | Hardware<br>Multiply | Hardware<br>Divide | Saturated<br>Math | DSP<br>Extensions | Floating<br>Point |

|------------|---------------------|----------------------|--------------------|-----------------------|----------------------|--------------------|-------------------|-------------------|-------------------|

| Cortex-M0  | ARMv6-M             | Von Neumann          | Most               | Subset                | Optional             | No                 | No                | No                | No                |

| Cortex-M0+ | ARMv6-M             | Von Neumann          | Most               | Subset                | Optional             | No                 | No                | No                | No                |

| Cortex-MI  | ARMv6-M             | Von Neumann          | Most               | Subset                | Optional             | No                 | No                | No                | No                |

| Cortex-M3  | ARMv7-M             | Harvard              | Entire             | Entire                | Optional             | Yes                | Yes               | No                | No                |

| Cortex-M4  | ARMv7E-M            | Harvard              | Entire             | Entire                | Optional             | Yes                | Yes               | Yes               | Optional          |

# **ARM Cortex-M0 Processor**

#### **Cortex-M0** Overview

- ARMv6-M Architecture

- Von-Neumann Architecture

- 32-bit Architecture

- Thumb technology

- Nested Vector Interrupt Controller (NVIC)

- AHB-Lite Master Interface

- Optional Ultra-low power Support

- Optional CoreSight-compliant Debug

- RTL is configurable

- Synthesizable

- Gate count 12 ~ 25K

### **Cortex-M0 Processor Programmers Model**

- The Cortex-M0 is designed to be programmed fully in C

- No need to write assembly code

- Thumb technology

- I6-bit and 32-bit instructions

- Set of processor core and memory-mapped registers are provided

- Architecturally defined memory map

- Forwards compatible with other M-profile processors

- Binary compatible

- In-order execution of instructions

- Multi-cycle instructions are abandoned and restarted on interrupt

- Multiple memory accesses (LDM/STM) are interrupted between transfers

- Deterministic instruction execution

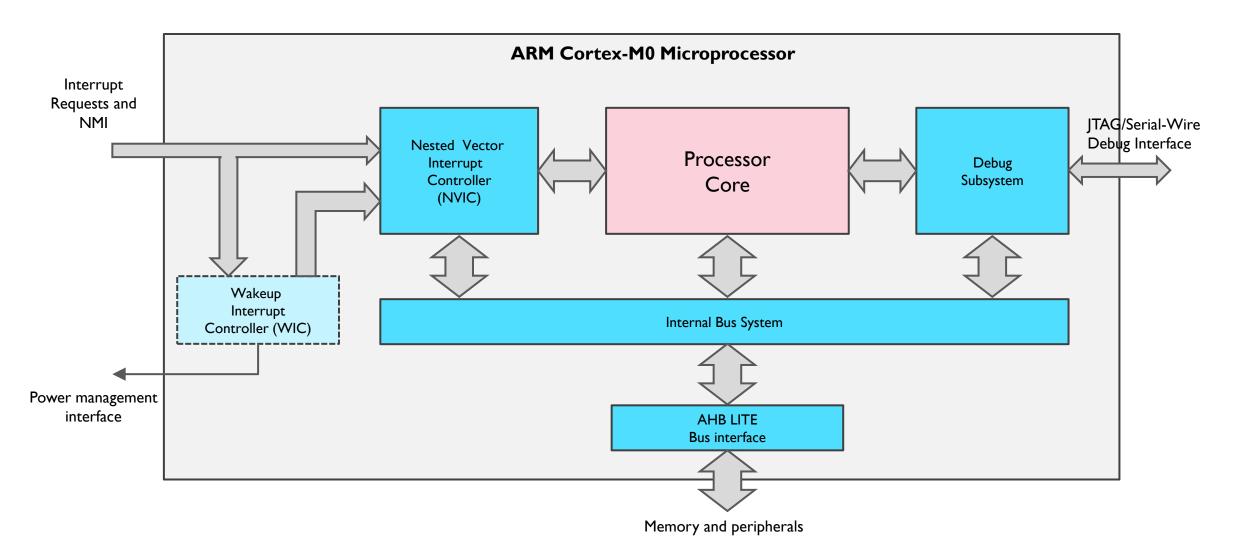

### Cortex-M0 Block Diagram

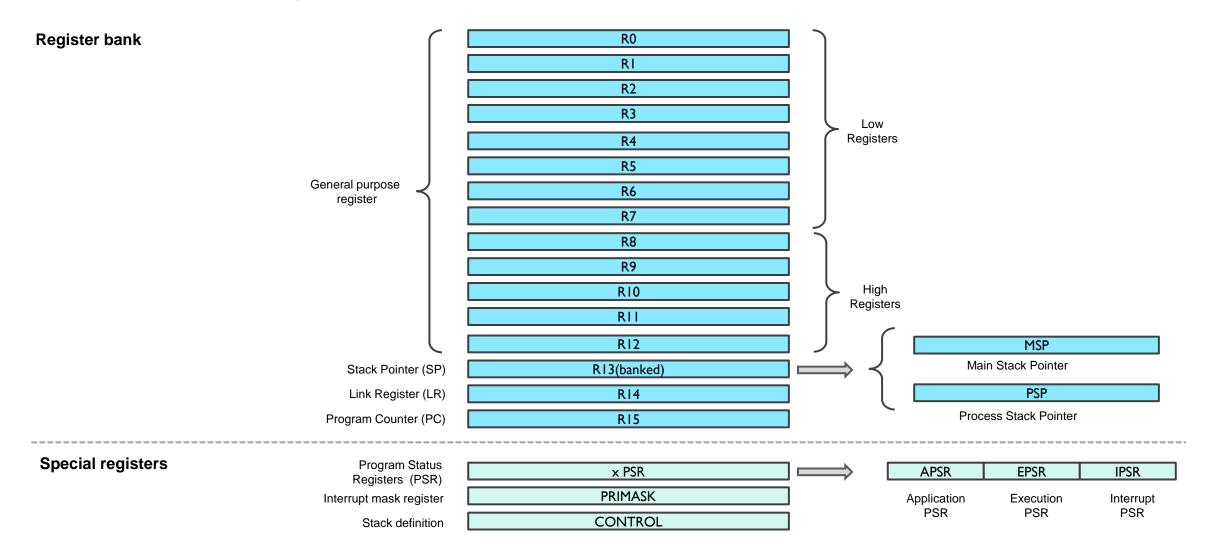

## **Cortex-M0 Registers**

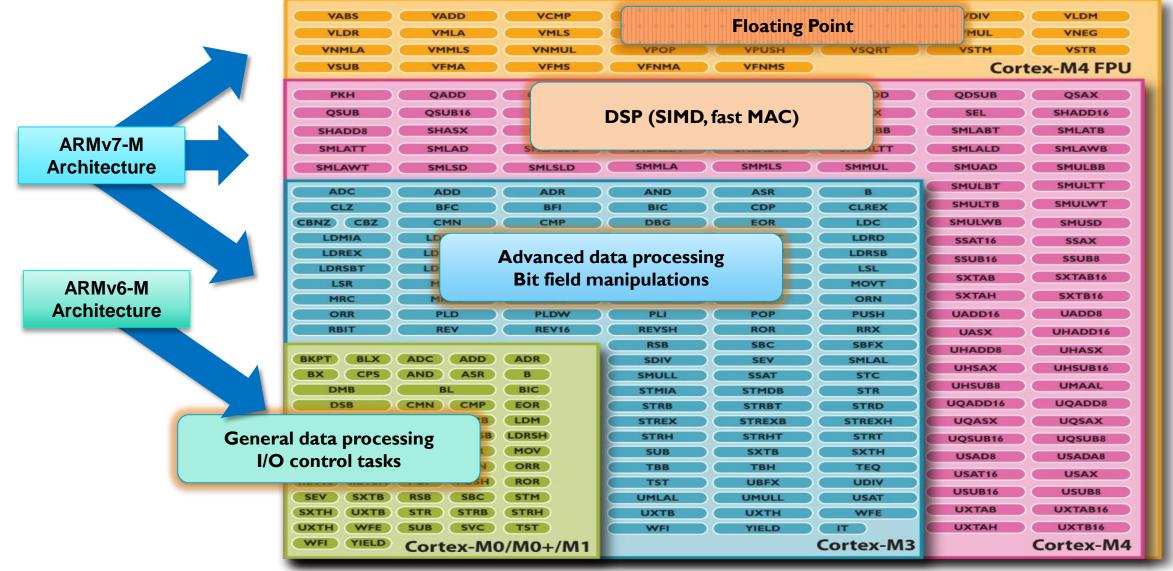

### **Reduced Instruction Set**

- Only 56 Instructions

- Mostly coded on 16-bit

- Operate on the 32-bit registers

- Option for fast MUL 32x32 bit in I cycle

- Instruction types

- Branch instructions

- Data-processing instructions

- Load and store instructions

- Status register access instructions

- Miscellaneous instructions

| BKPT BLX    | ADC ADD ADR      |

|-------------|------------------|

| BX CPS      | AND ASR B        |

| DMB         | BL BIC           |

| DSB         | CMN CMP EOR      |

| ISB         | LDR LDRB LDM     |

| MRS         | LDRH LDRSB LDRSH |

| MSR         | LSL LSR MOV      |

| NOP REV     | MUL MVN ORR      |

| REV16 REVSH | POP PUSH ROR     |

| SEV SXTB    | RSB SBC STM      |

| SXTH UXTB   | STR STRB STRH    |

| UXTH WFE    | SUB SVC TST      |

| WFI YIELD   | Cortex-M0/M0+/M1 |

## Cortex-M: binary upwards compatibility

AKM

# **ARM Cortex-M0 Processor**

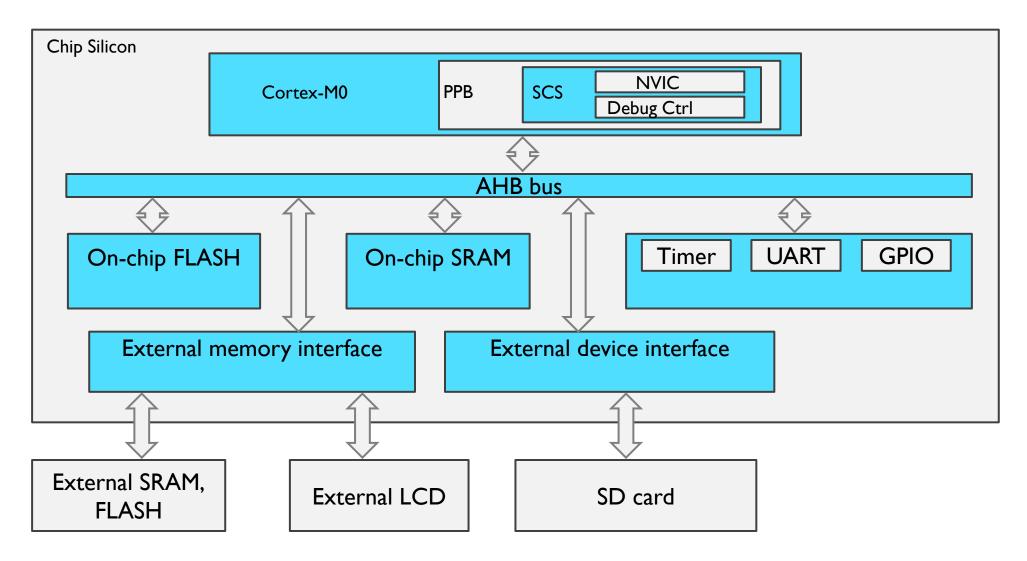

# Memory Architecture

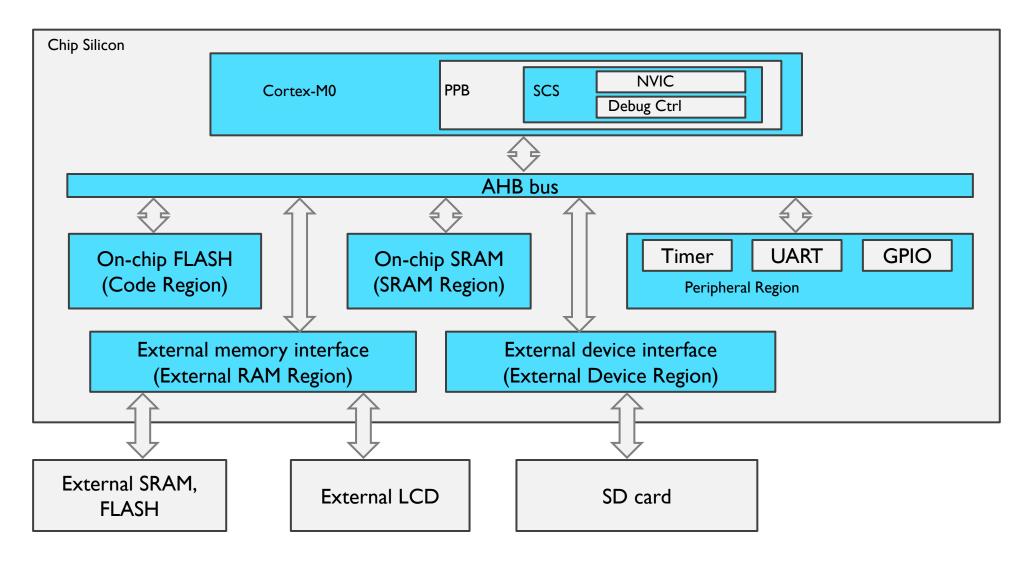

## Cortex-M0 Memory Map (Example)

## Cortex-M0 Memory Map (Example)

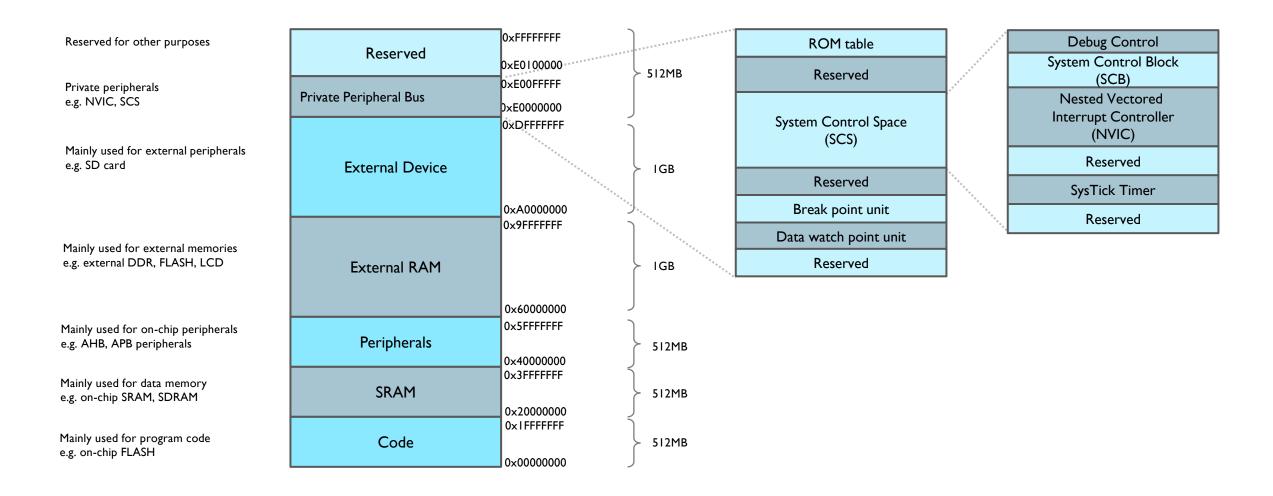

## Cortex-M0 Memory Map

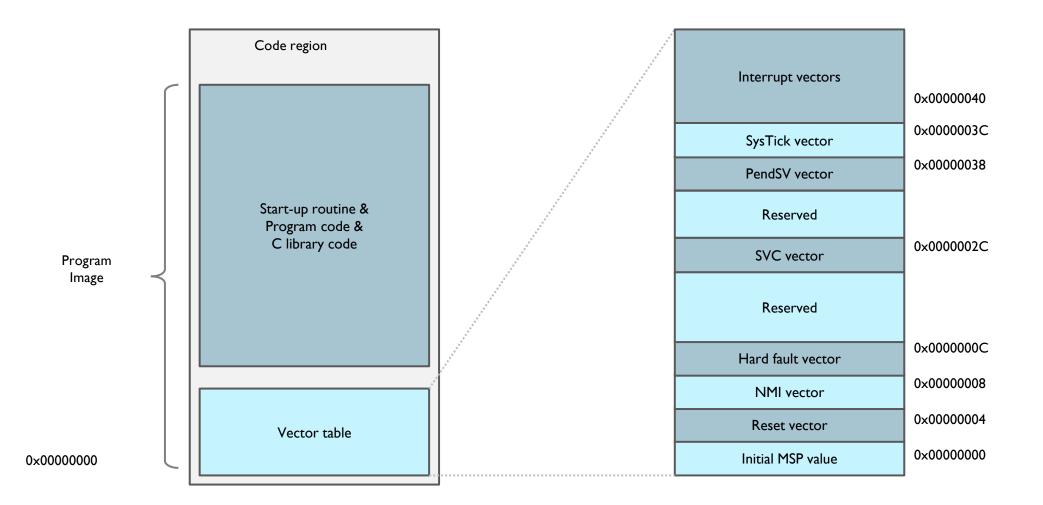

## Cortex-M0 Program Image

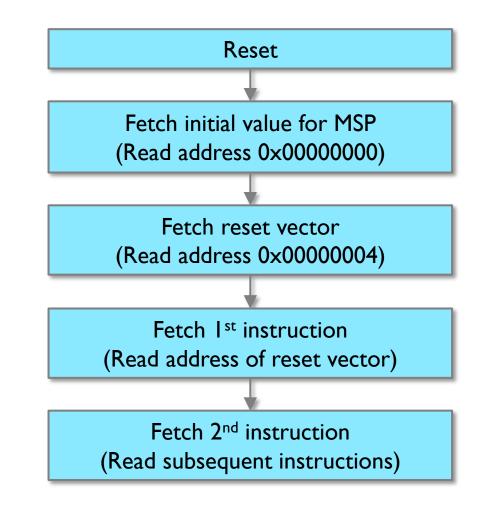

#### Cortex – M0 Reset Behaviour

- After reset:

- I. First reads the initial MSP value;

- 2. Then reads the reset vector;

- 3. Branches to the starting of the programme execution address (reset handler);

- 4. Subsequently executes program instructions.

### Cortex M0 Design Start

- Fixed configuration of the Cortex-M0 processor

- Low cost access to Cortex-M0 processor technology by offering a subset of the full product.

- Pre-configured and obfuscated, but synthesizable, Verilog version of the full Cortex-M0 processor

- Fully working version of the Cortex-M0 processor

- Used as the basis for production hardware and software designs.

- Gate count is ~16K

- Cortex M0 Processor gate count is 12k to 26K depending on the configuration

#### Cortex M0 Design Start vs Full Cortex M0

| Feature                                        | Full Cortex-M0 processor                                                                       | Cortex-M0 DesignStart process              |  |  |

|------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------|--|--|

| Verilog code                                   | Commented plain-text RTL.                                                                      | Flattened and obfuscated RTL.              |  |  |

| AMBA™3 AHB-Lite<br>interface                   | Master and optional slave<br>ports.                                                            | Master port only.                          |  |  |

| ARMv6-M instruction set                        | — Identical ARMv6-M                                                                            | I instruction set support. —               |  |  |

| Fast/small multiplier options                  | Fast single or small 32-cycle.                                                                 | Small 32-cycle multiplier only.            |  |  |

| Nested vectored interrupt<br>controller (NVIC) | 1 to 32 interrupt inputs.                                                                      | 16 interrupt inputs only.                  |  |  |

| Wake-up Interrupt<br>Controller                | Optional.                                                                                      | None.                                      |  |  |

| Architectural clock gating                     | Optional.                                                                                      | None.                                      |  |  |

| 24-bit system timer<br>(SysTick)               | Optional reference clock.                                                                      | Core clock source only.                    |  |  |

| Hardware debugger<br>interface                 | Optional Serial-Wire or JTAG.                                                                  | None.                                      |  |  |

| Hardware debug support                         | Optional single step with up to<br>four breakpoints, up to two<br>watchpoints and PC sampling. | None.                                      |  |  |

| Low-power signaling and<br>domains             | Optional state-retention power<br>domains and power control<br>signaling.                      | SLEEPING, TXEV and RXEV<br>signaling only. |  |  |

**ARM**

- Consider you have a simple Cortex M0 based Micro-controller with the following memory map

- Internal SRAM I KB Starting Address 0x0000 0000

- A LED Peripheral One word Address 0x5000 0000

- We will write assembly program to toggle the LEDs and simulate the program

- We will analyse the resulting binary file and the disassembly file

- In the Next Section we will see how to design AHB-Lite Compliant LED Peripheral